基于FPGA的简易数字频率计的设计(论文)

1.无需注册登录,支付后按照提示操作即可获取该资料.

2.资料以网页介绍的为准,下载后不会有水印.资料仅供学习参考之用.

密 惠 保

摘 要

本设计是基于FPGA的一个简易数字频率计,利用Verilog硬件描述语言设计实现了频率计内部功能模块,采用了等精度测量的方法,并结合NIOS软核CPU嵌入FPGA,构成SOPC系统,利用NIOS软核对数据浮点运算处理,管理人机交换界面实时显示,跟传统FPGA+单片机的多芯片系统方案相比更加灵活,系统体积小和功耗小等优势,具备软硬件在系统可编程的功能。

本设计测量频率的方法采用的是等精度测量法,相比直接测频法和测周法有精度更高的特点。前端信号输入调理采用宽带放大器AD811对微弱信号进行放大,经过比较器整形调理后,FPGA进行采用测量,系统实时性好,精度高。

关键词:等精度 频率计 FPGA NIOS Verilog

The Design Of Simple Digital Frequency Meter Base On FPGA

ABSTRACT

The design is based on FPGA digital frequency of a simple plan, use Verilog hardware design realized the frequency of internal function module, the accuracy of the measurement method, etc NIOS and FPGA, soft nuclear CPU embedded systems, using the SOPC constitute NIOS soft check data management man-machine floating point calculations, exchange, with real-time display interface chip traditional FPGA + MCU solutions, system is much more flexible than small volume and low consumption, have advantages of hardware and software systems in programmable functions.

This design method of measuring frequency by measuring method is compared with direct frequency measurement method, and the measuring accuracy of ZhouFaYou characteristics. Front-end signal input by AD811 amplifier to recuperate broadband amplification, weak signal by comparator plastic, after using measurements on FPGA, system of good real-time, high precision.

Key words: Equal precision Frequency counter FPGA NIOS Verilog

[来源:http://think58.com]

目 录 12000字

摘 要 I

ABSTRACT II

1 概 述 1

2 系统方案分析及比较选择 3

2.1 方案构想 3

2.2 方案比较及选用依据: 4

3 工作原理及其系统框图 5

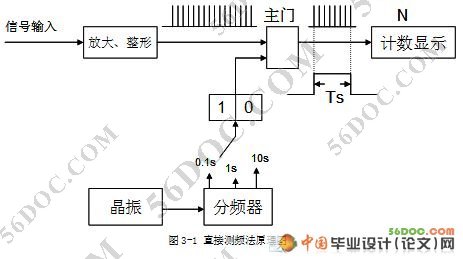

3.1 计数式直接测频法 5

3.2 计数式直接测周期 6

3.3 等精度测量原理 7

4 硬件系统实现 10

4.1 硬件系统原理图 10

4.1.1放大电路的选择 10

4.1.2 整形电路 13

4.2 FPGA控制电路 15

4.2.1 FPGA芯片选型 15

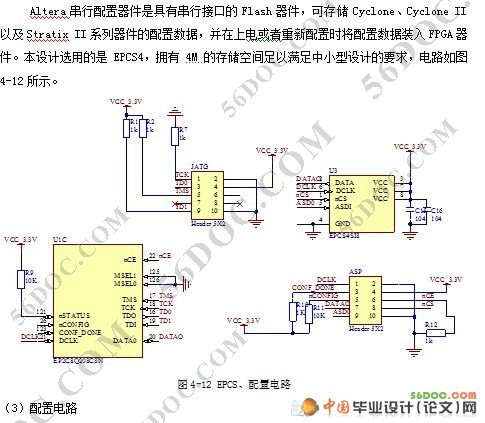

4.2.2 FPGA最小系统搭建 16

4.3 FPGA内部模块 19

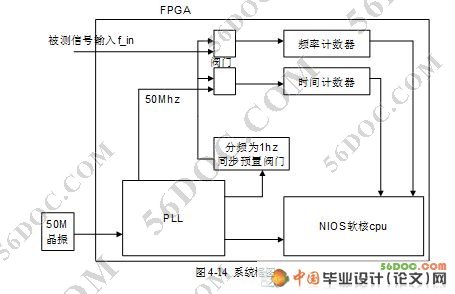

4.3.1系统总体框图 19

4.3.2 同步预置模块 20

4.3.3 频率计数模块、时间计数模块 21

4.3.4 数据输出模块,计数器清零模块 21

5 软件系统实现 23

5.1 主程序框图 23

5.2 NIOS II 软核 23

5.3.NIOS外部接口与内部介绍 24

5.3.1 nios软核原理框图 24

5.3.2 nios软核外部接口 24

6 遇到问题,分析问题,解决问题 25

6.1 输入阻抗问题 25

6.2 放大器选择问题 25

7 电路抗干扰措施 26

8 系统指标测试 27

9 结束语 28

参考文献 29

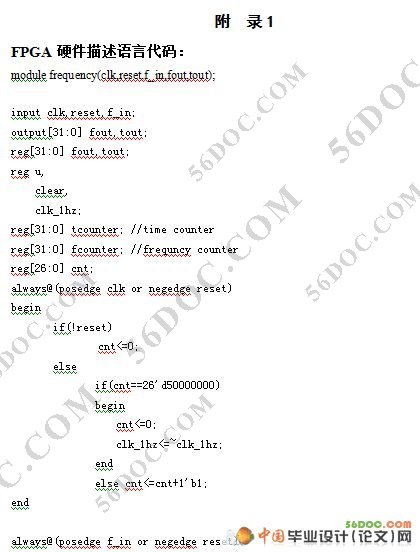

附录1:FPGA硬件描述语言代码 30

附录2:NIOS C语言程序代码 33

谢 辞 40

[资料来源:http://think58.com]