基于FPGA的高精度数字频率计设计

以下是资料介绍,如需要完整的请充值下载.

1.无需注册登录,支付后按照提示操作即可获取该资料.

2.资料以网页介绍的为准,下载后不会有水印.资料仅供学习参考之用.

密 惠 保

1.无需注册登录,支付后按照提示操作即可获取该资料.

2.资料以网页介绍的为准,下载后不会有水印.资料仅供学习参考之用.

密 惠 保

资料介绍:

基于FPGA的高精度数字频率计设计(任务书,开题报告,论文13000字)

摘 要

数字频率计是一种用来测量信号频率,并将所测结果进行十进制数字显示的测量仪器,如今已广泛应用于研究生产等各领域。相较于通过硬件设计所带来的器件复杂、连线困难等问题,运用以FPGA现场可编程门阵列为核心的设计方式不仅极大地简化了整个系统,同时还提升了系统的可靠性。

本次设计是以Altera Cyclone V SE 5CSEMA5F31C6N device芯片为核心,运用VHDL语言设计了一个能进行自动换挡的六档数字频率计,并具有秒表功能。所设计的频率计高位为档位,显示数字为0、1、2、3、4、5分别代表100、101、102、103、104、105档(基本单位:HZ),同时显示三位数字代表所测频率的高三位有效数字。

本文介绍了一种以FPGA为核心,运用硬件描述语言VHDL进行编程的数字频率计的设计方法,通过在软件QuartusⅡ上编写程序,然后对其编译、仿真和调试,均顺利通过且符合设计要求后,最后下载到实验箱的FPGA芯片上从而进行实现。其优点是简化了整个系统在一块FPGA芯片上,频率计体积很小,性能很高,可靠性很强,而且便于修改。

关键词:数字频率计;FPGA;VHDL

Abstract

[资料来源:http://think58.com]

Digital frequency meter is a kind of used to measure the signal frequency, and the measured results for decimal digital display measuring instrument,now has been widely used in research and production fields.Contrast through hardware design of the device is complex and difficult problems such as attachment,use the field programmable gate array FPGA as the core of design method not only greatly simplifies the whole system, and improve the reliability of the system.

This design is based on Altera Cyclone V SE 5CSEMA5F31C6N device chip as the core, the use of VHDL language design can be a six-speed automatic shifting digital frequency meter, and has a stopwatch function.Designed for the high-frequency meter stalls, shows the number of 0、1、2、3、4、5 representing 100、101、102、103、104、105 file (the basic unit: HZ), while the three-digit display high representative three significant digits of the measured frequency.

This article describes a FPGA as the core, using VHDL hardware description language programming design method of digital frequency meter,through the software Quartus Ⅱ program, then the compiler, simulation and debugging, all pass and comply with the design requirements, finally downloaded to the FPGA chip to implement experiment box.Its advantage is to simplify the system on a FPGA chip, the frequency meter is small volume, high performance, reliability, and easy to modify. [资料来源:http://think58.com]

Key Words:Digital frequency meter;FPGA;VHDL

[资料来源:THINK58.com]

目 录

摘 要 I

Abstract II

第1章 绪论 1

1.1国内外研究现状 1

1.2目的及意义 2

第2章 FPGA和VHDL及软件简介 3

2.1 FPGA简介 3

2.2 VHDL简介 4

[资料来源:http://think58.com]

2.3软件简介 4

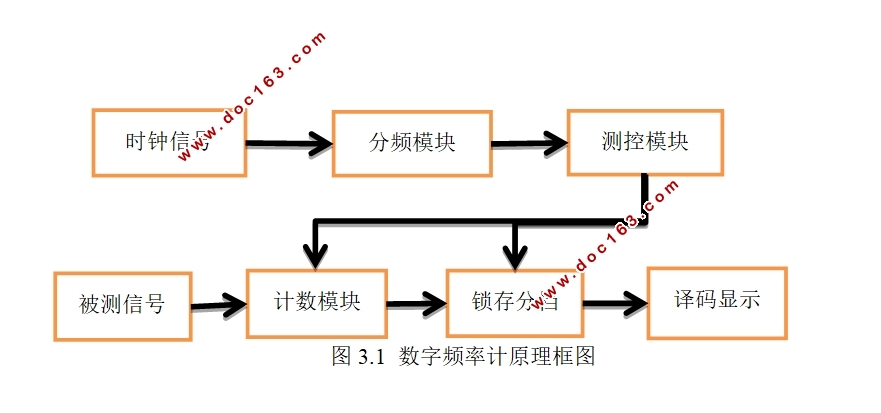

第3章 频率计设计原理 6

3.1设计要求 6

3.2测频原理 6

3.3设计方案 7

第4章 频率计功能模块设计 9

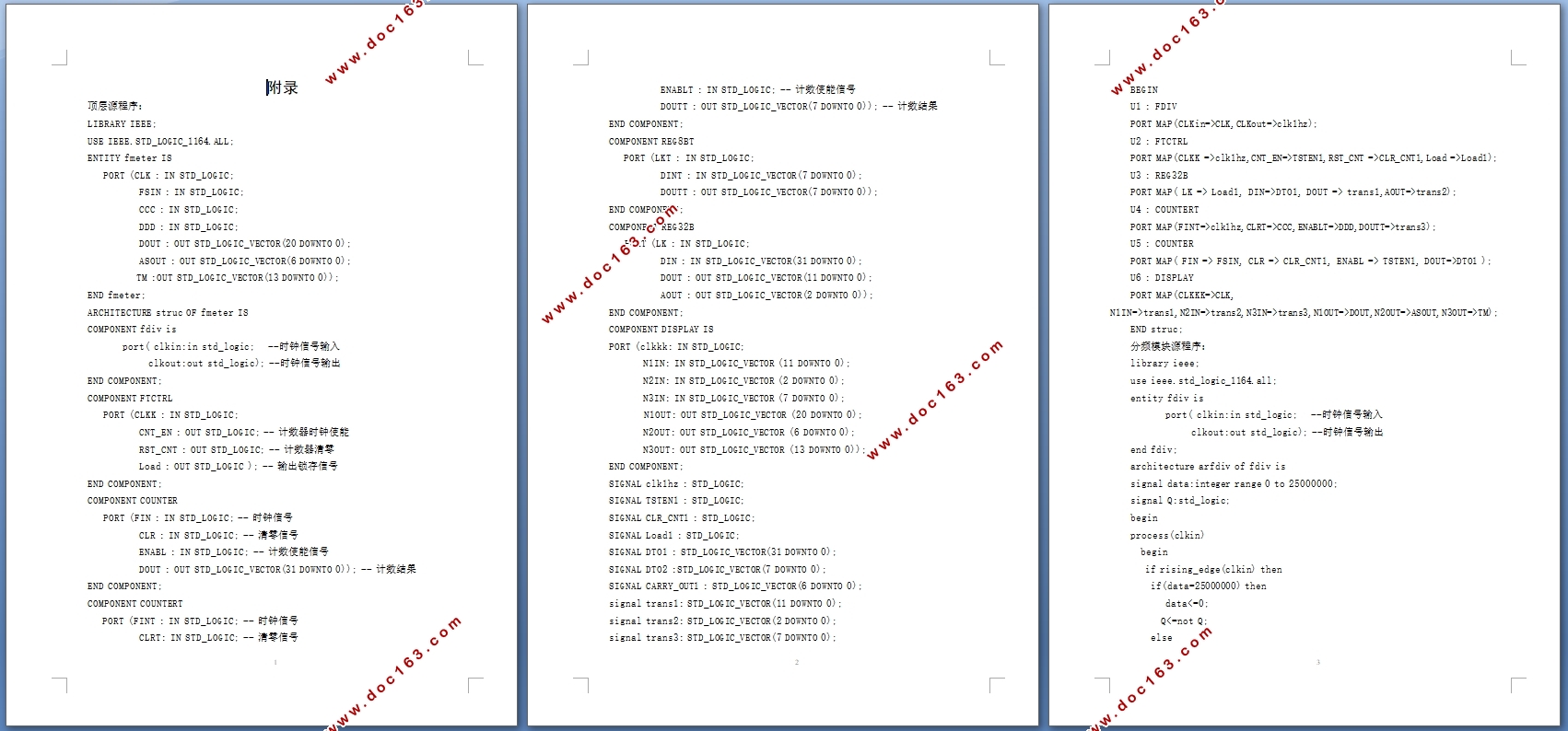

4.1分频模块 9

4.2测控模块 9

4.3计数模块 10

4.3.1十进制计数器 10

4.3.2八位十进制计数器 12

4.4锁存分档模块 12

4.5译码显示模块 14

第5章 秒表设计 15

第6章 调试与分析 16

第7章 总结与体会 18

参考文献 19

致 谢 21

[资料来源:THINK58.com]